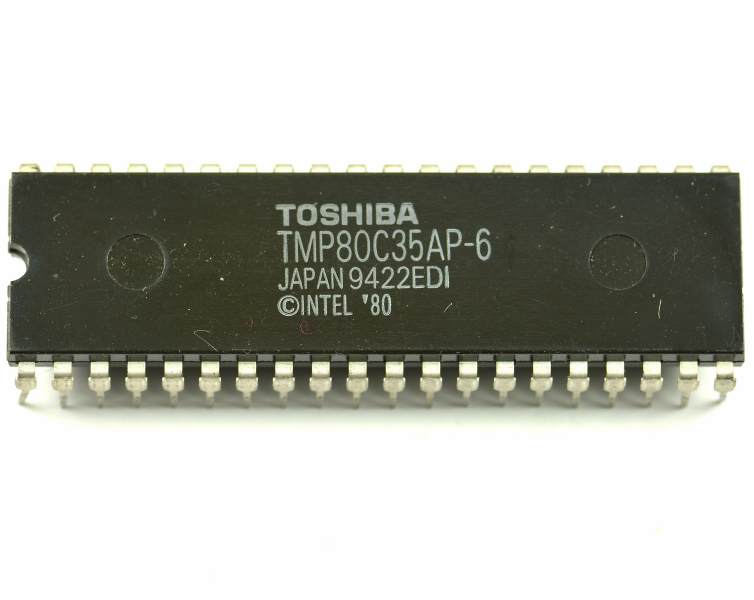

Toshiba TMP80C35

Definition

The Toshiba TMP80C35 is an 8-BIT MICROCONTROLLER from the TLCS-48C family, manufactured using CMOS (Silicon Gate) technology. It is intended as a “no on-chip ROM” version of the same logic platform: it keeps the internal 8-BIT architecture, on-chip RAM, and basic peripherals, but delegates program storage to external devices (typically EPROM).

In practice, the TMP80C35 is used when you want the same compatibility/structure of a microcontroller with integrated ROM, but with greater flexibility during development and debugging (firmware on a replaceable external memory).

8-bit internal architecture (what is inside)

The device integrates the fundamental functions of a “single-chip” microcontroller, in a layout very typical of the 48/35 derivatives:

Internal 8-BIT CPU (8-bit parallel architecture).

On-chip data RAM: 64 × 8 bytes, used for variables and working areas.

Total I/O lines: 27 (quasi-bidirectional ports and ports with alternate functions).

8-BIT TIMER / EVENT COUNTER for time-base, event counting, and basic timing.

Compared to the variant with integrated ROM, the key difference is the absence of on-chip program ROM: instruction fetch is performed from external program memory when configured for external access.

Main difference: no on-chip ROM and external program memory

The TMP80C35 is conceptually equivalent to a TMP80C48A, but without internal program ROM. This implies:

The need for an external EPROM (or other memory) to store the firmware.

Easier development iterations (you swap the EPROM without replacing the MCU).

The option to use the device in emulation/debug scenarios where external access is advantageous.

At board level, this introduces the typical bus-related signals for external memory (read/write strobes, program fetch enable, address latching).

Performance and power (practical indicators)

In typical versions of the family:

Instruction-cycle timing is indicated as 1.36 µs (nominal temperature and supply conditions for the standard version) and 2.5 µs for the “-6” variant with wider supply specifications.

CMOS technology targets low power, including power-saving modes such as POWER DOWN and HALT/IDLE (depending on configuration).

These features make the device suitable for embedded control with predictable timing and reduced power requirements, especially compared with older non-CMOS implementations.

Signals and board integration (what is needed around the chip)

A typical use requires:

VCC (5 V) and ground, with decoupling.

Oscillator using XTAL1/XTAL2 (crystal or external source).

RESET for initialization.

I/O lines to sensors/actuators.

If external memory is used: data bus DB0–DB7 and control signals for external EPROM/RAM access (including program fetch and address latch signals).

Sketch of the most important connections

┌──────────────────────────────┐

│ POWER │

│ VCC / GND + decoupling │

└──────────────┬───────────────┘

│

▼

┌──────────────────┐

│ TOSHIBA TMP80C35│

│ 8-BIT CMOS MCU │

│ RAM 64×8 │

│ 27 I/O + TIMER │

└───────┬──────────┘

│

├────────► I/O → sensors / keys / LEDs / relays

│

├────────► XTAL1/XTAL2 + RESET

│

└────────► (opt.) external BUS → EPROM (program) + RAM (data)

Table 1 – Identification data and specifications (English)

| Characteristic | Typical value |

|---|

| Device | Toshiba TMP80C35 |

| Class | 8-BIT MICROCONTROLLER ( TLCS-48C family) |

| Technology | CMOS (Silicon Gate) |

| On-chip program ROM | Not present (external program memory) |

| On-chip RAM | 64 × 8 |

| I/O lines | 27 |

| Timer | 8-BIT TIMER / EVENT COUNTER |

| Typical package | 40-PIN DIP (related variants also in compact packages) |

Table 2 – Operational and design aspects (English)

| Aspect | Practical meaning |

|---|

| Firmware on external EPROM | More flexible development and debugging vs on-chip mask ROM |

| External bus signals | Required for program fetch and (if used) external data access |

| Low-power modes | Power reduction via POWER DOWN and HALT/IDLE |

| Application timing | Reliable time-base through the TIMER and predictable instruction cycles |

| Typical use | Embedded control, state machines, digital I/O, sequences and timing |

![]() Toshiba TMP80C35AP-6

Toshiba TMP80C35AP-6