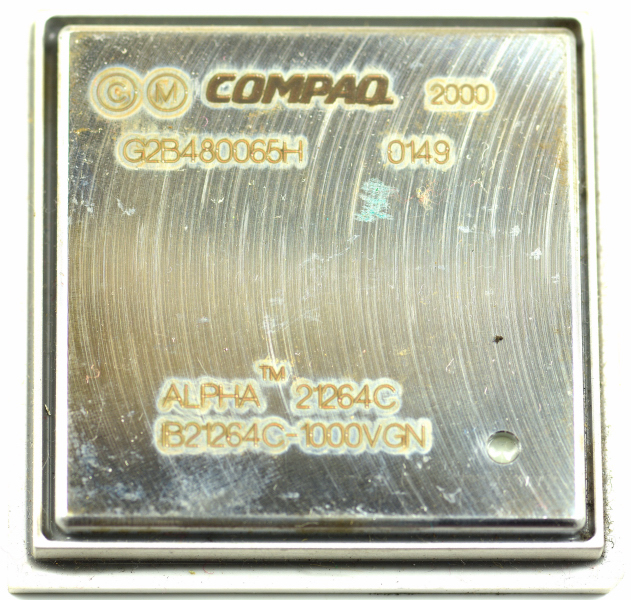

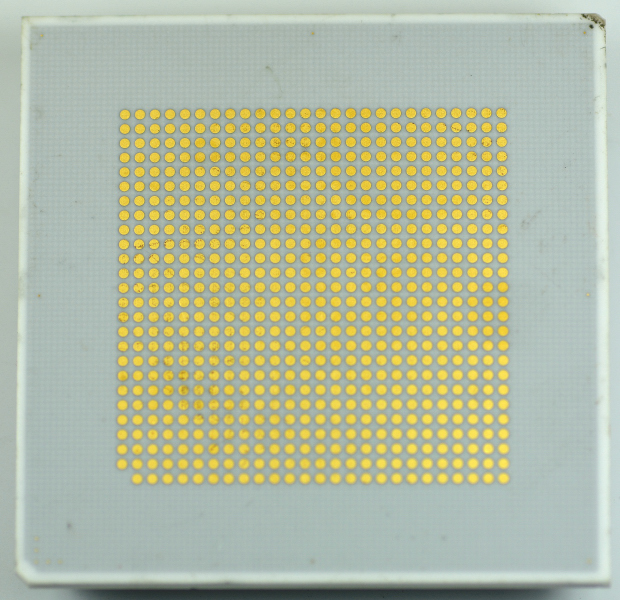

Compaq Alpha 2164C – IB2164C-1000VGN 1 GHZ CPU for the ES45 server, with split L1 cache and 8 MB DDR L2 cache

Definition

The Compaq Alpha 2164C (CPU IB2164C-1000VGN) is a server-class 64-bit microprocessor from the Alpha family, installed in Compaq systems (specifically the ES45 server). It is designed for enterprise and technical workloads where data-access latency, memory bandwidth, and the ability to sustain high throughput on large code and dataset footprints are critical.

The stated operating specifications for this variant are: 1 GHZ frequency, 128K L1 cache (organized as 64K + 64K), and 8 MB Dual Data Rate L2 cache.

Frequency: 1 GHZ and “server-class” positioning

A 1 GHZ clock places this CPU in the high end of late-cycle Alpha platforms, where the goal is to maximize single-thread performance and overall throughput on server workloads. In practice, real performance depends not only on clock rate but also on the balance between cache, the memory subsystem, and the server’s system interconnect.

L1 cache: 128K (64K + 64K) and practical meaning

The 128K (64K + 64K) L1 cache is a split structure:

Practically, this separation reduces contention between code fetch and data accesses, improving performance stability when the workload alternates instruction execution with memory reads/writes.

L2 cache: 8 MB DDR and implications

The 8 MB DDR L2 cache is central to platform behavior:

8 MB capacity tends to reduce misses to main memory on large datasets and server workloads (buffers, large working sets, persistent data structures).

Dual Data Rate indicates an interface designed to increase effective bandwidth between the CPU and L2, reducing a common bottleneck in high-frequency systems.

Practically, a large and “fast” L2 improves under-load predictability and reduces sensitivity to main-memory latency.

Integration in the ES45 server: a platform view

The fact that the CPU is installed in the ES45 server matters because, in server architectures, perceived performance depends strongly on:

Memory controller behavior and arbitration policies.

RAM configuration and the I/O subsystem (storage and networking).

Coherence between core frequency and the platform’s ability to feed the CPU with data (cache and memory).

In other words, the Alpha 2164C should be viewed as “CPU + cache + platform”, not just nominal clock speed.

Sketch of the most important connections

server platform (memory + I/O + system controller)

┌──────────────────────────────────────────────────────────┐

│ ES45 server / system logic │

│ RAM, storage, networking, interrupts, timing, backplane │

└───────────────────────────────┬──────────────────────────┘

│

▼

┌─────────────────────────────┐

│ Alpha 2164C │

│ IB2164C-1000VGN @ 1 GHZ │

│ L1 cache 64K + 64K │

│ L2 cache DDR 8 MB │

└─────────────┬───────────────┘

│

├────────► RAM (via system controller)

└────────► I/O (storage/network via platform)

Table 1 – Identification data and specifications

| Characteristic | Indicative value |

|---|

| Device | Compaq Alpha 2164C |

| CPU / part number | IB2164C-1000VGN |

| Deployment platform | ES45 server |

| Frequency | 1 GHZ |

| L1 cache | 128K (64K + 64K) |

| L2 cache | Dual Data Rate 8 MB |

Table 2 – Operational and design considerations

| Aspect | Practical meaning |

|---|

| 1 GHZ | High performance, but dependent on cache and the platform memory subsystem |

| Split L1 64K + 64K | Less contention between instructions and data, good stability on mixed workloads |

| 8 MB DDR L2 | Reduces main-memory accesses on large working sets; increases bandwidth to the second-level cache |

| ES45 server deployment | Performance depends on memory controller, RAM configuration, and I/O (storage/network) |

| Server-class profile | Optimized for throughput and sustained loads rather than “desktop” scenarios |

![]() Compaq Alpha 2164C

Compaq Alpha 2164C