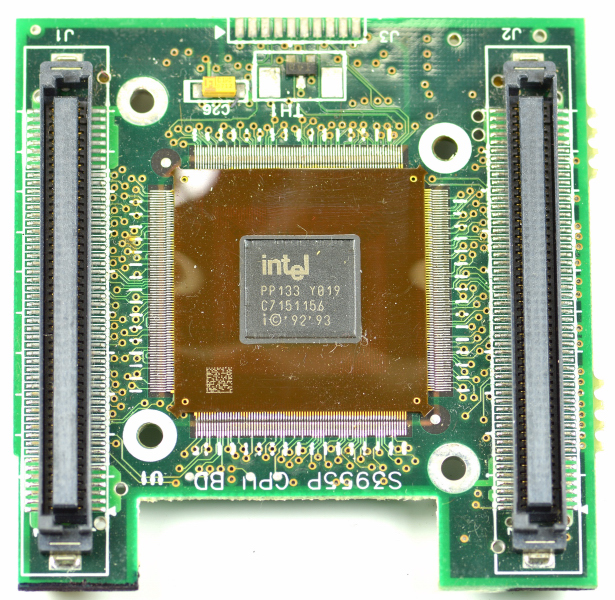

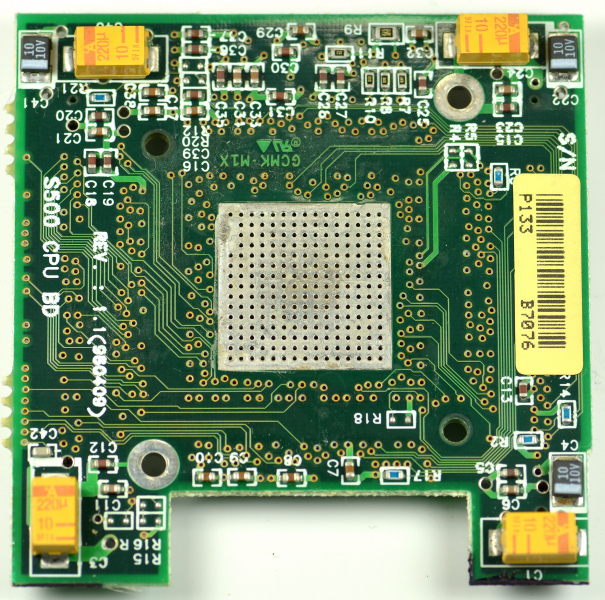

Packaging: TCP (Tape Carrier Package) and notebook implications

The Tape Carrier Package prioritizes:

Low profile and reduced footprint for portable designs.

Connections suited to direct motherboard mounting under space constraints.

More “industrial” integration than socketed PGA packages, often improving mechanical robustness and density.

Operationally, TCP also influences thermal design: the contact surface and heat-removal method (heatsink plate, spreader, airflow) must be compatible with a flat package placed close to the board.

Frequencies: 133 MHZ core and 66 MHZ board

Frequency: 133 MHZ

The CPU runs at 133 MHZ, a typical value for mid-1990s mobile Pentium-class parts.

Board frequency: 66 MHZ

The 66 MHZ board frequency corresponds to the platform bus clock. In practice, the CPU reaches 133 MHZ via an internal multiplier.

Clock: 2×

The 2× value confirms a 2:1 multiplier ratio between the board clock and the core clock (66 → 133). This approach increases core performance without requiring the chipset and memory to operate at the same higher frequency.

Cache: 16K + 16K (split L1)

The stated 16 + 16 K cache is a split L1 cache:

16K for instructions.

16K for data.

In practice, splitting reduces contention between code fetch and data accesses, improving smoothness on mixed workloads (typical of desktop operating systems of the era and office applications).

Bus: 64-bit and bandwidth impact

Bus: 64-bit

A 64-bit data bus increases potential bandwidth between the CPU and chipset/memory versus narrower buses. Operationally:

it improves burst transfers and cache fill behavior

real performance still depends on notebook chipset choice, RAM configuration, and platform latency

Integration technology: transistor count, process, and voltage

Transistors: 3.3 million

A count of roughly 3.3 million transistors is consistent with early Pentium-class CPUs featuring an integrated FPU and split L1 cache.

Micron: 0.35u

The 0.35 µm process places this CPU in a technology era where frequency and power are managed with significant trade-offs between performance and heat.

Voltage: 2.9 V

A 2.9 V core voltage is typical for many Pentium implementations of that period. In practice, voltage and process define the thermal envelope and notebook power-regulation requirements (VRM and power management).

Sketch of the most important connections

66 MHZ board bus + notebook chipset (RAM/I-O) ┌──────────────────────────────────────────────────────────┐ │ notebook motherboard + chipset │ │ RAM, BIOS/ROM, I/O, storage controller, power mgmt │ └───────────────────────────────┬──────────────────────────┘ │ 64-bit data bus ▼ ┌─────────────────────────────┐ │ Intel PP133 │ │ TCP package (notebook) │ │ 133 MHZ core (2× on 66) │ │ L1 16K I + 16K D │ └─────────────┬───────────────┘ │ ├────────► RAM (via chipset) └────────► I/O (storage/video/network via platform)

Table 1 – Identification data and specifications

| Characteristic | Indicative value |

|---|---|

| Device | Intel PP133 |

| Class | Mobile Pentium-class CPU in TCP |

| Packaging | TCP (Tape Carrier Package) |

| Core frequency | 133 MHZ |

| Board frequency | 66 MHZ |

| Multiplier / clock | 2× |

| Cache | 16K + 16K |

| Data bus | 64-bit |

| Transistors | 3.3 million |

| Process | 0.35 µm |

| Voltage | 2.9 V |

Table 2 – Operational and design considerations

| Aspect | Practical meaning |

|---|---|

| TCP for notebooks | Low-profile, compact integration on portable motherboards |

| 133 MHZ on 66 MHZ board | Higher core performance without raising chipset/RAM requirements excessively |

| 2× multiplier | Keeps the platform bus clock more manageable while boosting core speed |

| Split L1 16K + 16K | Reduces instruction/data contention, improving responsiveness on mixed workloads |

| 64-bit bus | Higher potential bandwidth, dependent on chipset and memory |

| 0.35 µm and 2.9 V | Era-typical performance/power trade-off with notebook thermal constraints |

| 3.3 million transistors | Integration sufficient for split L1 and internal units (including FPU in Pentium-class) |