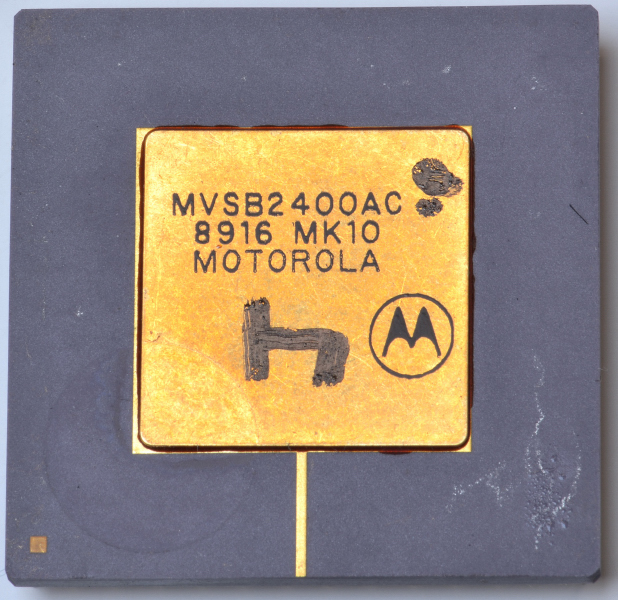

Motorola MVSB2400

Definition

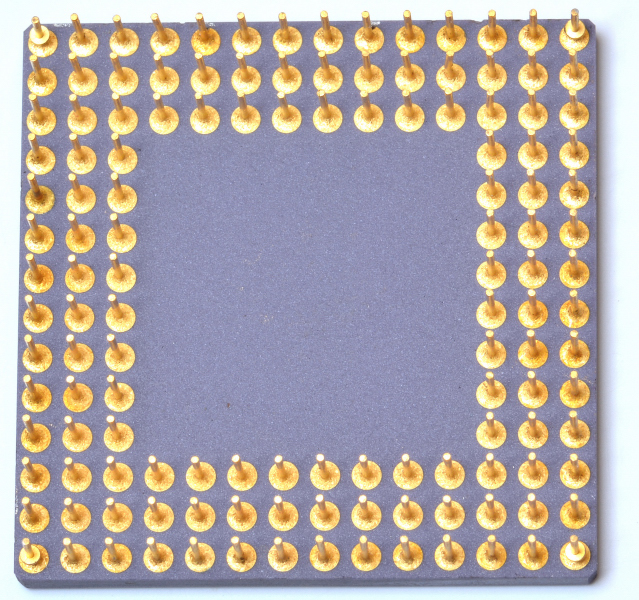

The Motorola MVSB2400 is a “VSBchip”: a VLSI device (implemented as a gate array in a 132-pin PGA package) designed to implement most of the functions required for a VSBbus (VME Subsystem Bus) interface in VMEbus/VSB systems. In practice, it integrates in a single chip much of the interface logic toward the VSBbus, including bus drivers, control-signal handling, and especially the address/data multiplexing required by the VSB architecture.

Context: VSBbus as a local extension of VMEbus

The VSBbus is described as a subset of the VMEbus used as a local extension bus: it allows a processor board to access additional memory and I/O on a “nearby” bus (typically on the P2 connector), reducing traffic on the global bus and improving overall system throughput. The VSB interface occupies 64 I/O pins on P2 and uses address/data multiplexing to achieve 32-bit functionality within that pin constraint.

Main function of the MVSB2400 (what it does in practice)

On many Motorola VME/VSB processor boards of that era, the MVSB2400 is used to:

Implement most of the logic required to support a VSBbus master interface using a single VLSI device and minimal external glue logic.

Integrate most of the bus drivers for the VSBbus and all the address/data multiplexing logic.

Provide (at the chip level) a slave capability as well, even though some boards using it may not support VSB slave accesses.

In other words: the board CPU and system logic delegate to the MVSB2400 the most repetitive “electrical and protocol” parts of VSB, making the local subsystem design simpler (and more compact).

Typical integration on VME/VSB boards

An explicit usage example appears on modules such as MVME135/136, where the VSBbus is implemented “through the use of the MVSB2400”. In that context, the board uses the MVSB2400 to expose the local bus on the P2 connector and attach memory or I/O expansions on VSB without saturating the main VMEbus.

Sketch of the most important connections

┌──────────────────────────────┐

│ VME CPU board (HOST) │

│ CPU + RAM + local logic │

└──────────────┬───────────────┘

│ local bus / internal signals

▼

┌──────────────────┐

│ MVSB2400 │

│ VSBchip │

│ drivers + A/D MUX│

│ master (slave*) │

└─────────┬────────┘

│ VSBbus on P2 connector (64 I/O pins)

▼

┌────────────────────────────────┐

│ VSB expansions (memory / I/O) │

│ local modules, peripherals, etc │

└────────────────────────────────┘

In parallel:

┌──────────────────────────────┐

│ Global VMEbus │

│ (backplane, other VME modules)│

└──────────────────────────────┘

* SLAVE capability may not be enabled/supported by the specific board.

Table 1 – Identification data and positioning (English)

| Characteristic | Typical value |

|---|

| Device | Motorola MVSB2400 (“VSBchip”) |

| Role | VSBbus interface for VMEbus/VSB systems |

| Implementation | Gate array in PGA package (132 pins) |

| Key function | Bus drivers + address/data multiplexing + control logic |

| Modes | Master support (typical), chip-level SLAVE capability (board-dependent) |

Table 2 – Operational and system aspects (English)

| Aspect | Practical meaning |

|---|

| VSBbus | Local extension bus (subset of VMEbus) for memory and I/O |

| P2 / pinout | VSB interface on P2 with a 64 I/O pin constraint |

| A/D multiplexing | Enables 32-bit functionality within the pin constraint |

| System benefit | Less traffic on the global VMEbus, higher overall throughput |

| Typical integration | Used on VME/VSB boards (e.g., MVME135/136) to implement VSB |

![]() Motorola MVSB2400

Motorola MVSB2400