Motorola MC68882

The Motorola MC68882 is an external FPU (floating-point unit) intended as a math coprocessor for the M68000 family, most commonly paired with the MC68020 and MC68030. Its role is to execute floating-point arithmetic and numeric conversions in hardware, delivering higher performance and accuracy than software emulation while preserving an integrated programming model: floating-point instructions are handled through the system coprocessor interface, often with overlapped execution alongside the integer CPU.

A key architectural point: the MC68882 is not a bus master. The host CPU fetches operands and stores results on behalf of the FPU, based on coprocessor requests. This simplifies system design and leverages the CPU data bus for fast transfers.

Capabilities and practical benefits

IEEE 754 compliance: full binary floating-point standard behavior (rounding modes, exceptions, NaN/Inf handling, etc.).

Dedicated instruction set: arithmetic operations plus a broad set of trigonometric and transcendental functions beyond the minimum IEEE scope.

Floating-point register file: 8 general-purpose registers (FP0–FP7) using 80-bit extended precision, reducing intermediate rounding error and improving numerical robustness.

High-speed conversions: dedicated hardware to convert between memory formats (single/double/extended, integers, packed BCD) and the internal extended format, lowering conversion overhead.

Concurrency: many FPU operations can proceed while the CPU continues executing integer instructions, with transparent synchronization when required.

Compatibility: instruction-set compatible with the MC68881 and often a drop-in replacement; the MC68882 adds performance enhancements (notably in pipelining/conversions).

System integration (coprocessor interface)

With MC68020/MC68030, interaction is based on the coprocessor protocol:

The CPU recognizes a floating-point instruction and forwards it via the coprocessor interface.

The FPU can request the CPU to perform supporting actions (effective address evaluation, operand fetch, result store).

Once requests are satisfied, the CPU can proceed while the FPU completes the numeric work, except when exceptions or dependencies require synchronization.

This makes the FPU an orthogonal ISA extension: from a programmer’s perspective, CPU + FPU behave close to a single logical processor.

Numeric formats and exception model

The MC68882 supports multiple numeric formats and a complete exception/context model suitable for virtual memory and multitasking: internal state can be saved/restored (for example via FSAVE/FRESTORE in the 68K environment), allowing an OS to preempt and resume tasks even while floating-point activity is in progress.

Sketch of the most important connections

┌──────────────────────────────┐

│ CPU MC68020/68030 │

│ data/address bus + MMU* │

│ coprocessor interface │

└──────────────┬───────────────┘

│ (CPU space / coprocessor protocol)

▼

┌──────────────────┐

│ MC68882 FPU │

│ FP regs + ALU │

│ conversion unit │

│ exceptions/CSR │

└─────────┬────────┘

│ (operand/result requests)

▼

┌────────────────────────────────┐

│ Memory and bus subsystem │

│ operands/results moved by CPU │

│ (FPU is not a bus master) │

└────────────────────────────────┘

* With MC68030 the MMU is on-chip; the FPU remains external to the MMU boundary.

Table – Identification data and specifications

| Parameter | Typical value |

|---|

| Device | Motorola MC68882 (FPU / math coprocessor) |

| Typical host CPUs | MC68020, MC68030 (M68000 family) |

| Floating-point standard | IEEE 754 (full implementation) |

| Registers | 8 floating-point registers (FP0–FP7), 80-bit extended precision |

| Supported formats | Integers (byte/word/long), real single/double/extended, packed BCD |

| Instruction set | Dedicated FP instructions, including trigonometric and transcendental functions |

| Concurrency | Often overlapped execution with the host CPU (instruction-dependent) |

| Bus mastering | No: host CPU moves operands/results |

| Host data bus | System-dependent (commonly used with 16/32-bit 68K systems) |

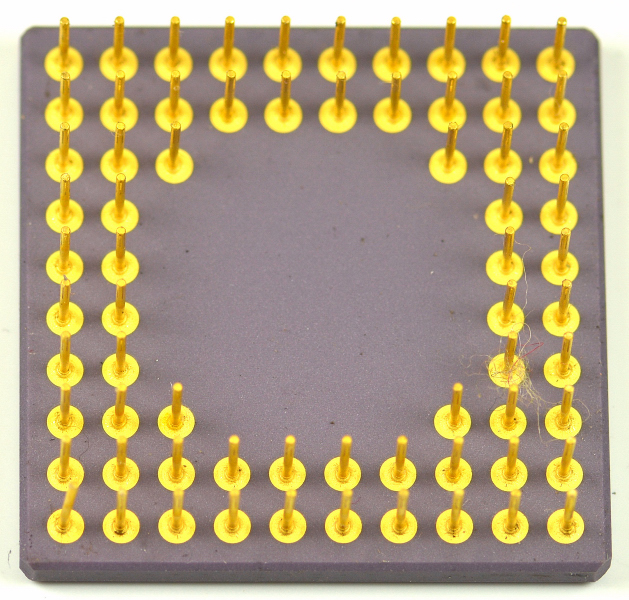

![]() Motorola MC68882RC50A

Motorola MC68882RC50A