| "Descrizione" by RS232 (2013 pt) | 2026-Jan-29 12:24 |

Review Consensus: 8 Rating: 8 Number of users: 1

| Evaluation | N. Experts | Evaluation | N. Experts |

|---|---|---|---|

| 1 | 6 | ||

| 2 | 7 | ||

| 3 | 8 | ||

| 4 | 9 | ||

| 5 | 10 |

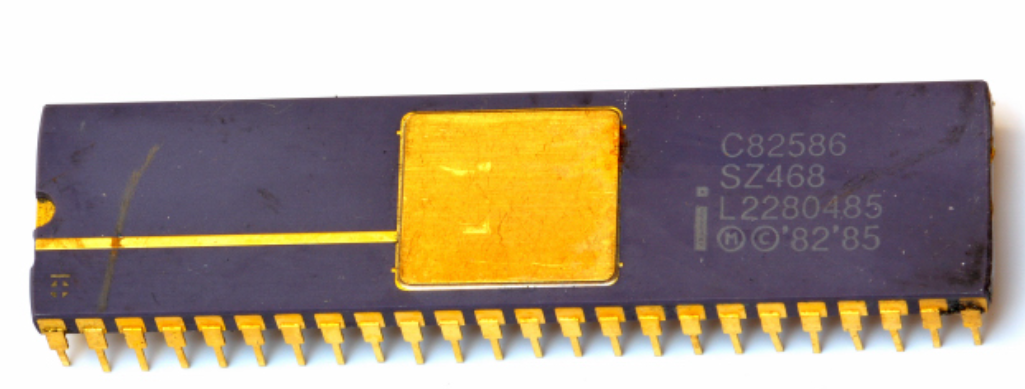

L'Intel C82586 era un Coprocessore LAN Ethernet immesso sul mercato nel 1982 e si inseriva nei sistemi 80186 e 80188.

Ethernet LAN coprocessor

Definizione

Un Ethernet LAN coprocessor è un circuito integrato che implementa (in larga parte) le funzioni di controllo del collegamento per una rete Ethernet, riducendo il carico della CPU host. Un dispositivo “tipo Intel 82586” lavora come coprocessore I/O: la CPU prepara strutture e comandi in memoria condivisa, poi il coprocessore gestisce in autonomia gran parte della trasmissione e ricezione dei frame, coordinando accessi DMA alla RAM e dialogando con la sezione fisica (transceiver/MAU) dell’Ethernet.

In termini pratici, il 82586 si colloca tra:

CPU host e RAM (dove risiedono buffer e descrittori)

Transceiver Ethernet (lato fisico, tipicamente 10 Mb/s in ambito IEEE 802.3 per la famiglia storica)

Perché serve (logica di sistema)

Senza un coprocessore LAN, la CPU dovrebbe:

Gestire byte-per-byte la copia dei pacchetti tra RAM e interfaccia di rete

Calcolare e verificare campi/controlli legati al frame (in modo fortemente dipendente dall’implementazione)

Gestire code di trasmissione, buffer di ricezione, retry e condizioni di contesa del mezzo

Un 82586-like sposta questa complessità su hardware e microcodice interno, offrendo:

DMA per trasferire blocchi di dati senza intervento continuo della CPU

Gestione strutturata di descrittori (command/tx/rx) in memoria

Funzionamento parallelo “CPU orchestration + coprocessore esecuzione” (entro i vincoli di banda memoria e sincronizzazione)

Architettura funzionale

Un controller tipo 82586 si può leggere come due insiemi di funzioni:

Receive unit: acquisisce frame dal lato fisico, li valida e li deposita in buffer RAM tramite descrittori di ricezione

Command/transmit unit: preleva comandi e buffer di trasmissione da RAM, costruisce il frame e gestisce l’invio sul mezzo, aggiornando stati e statistiche in memoria

Il punto cruciale è il modello a memoria condivisa: la CPU non “spinge” direttamente i pacchetti al chip con I/O programmato, ma imposta strutture dati (liste, ring, puntatori) che il coprocessore percorre e aggiorna.

Modello di comunicazione CPU–coprocessore (shared memory)

La CPU tipicamente svolge queste attività:

Inizializza puntatori e strutture di controllo (root/config)

Alloca e collega descrittori e buffer (tx e rx)

“Sveglia” il coprocessore quando ha inserito nuovi comandi (segnale di channel attention o equivalente, a seconda della scheda)

Legge stato/interrupt e ricicla buffer completati

Il coprocessore:

Legge i comandi dalla lista (Command Block List)

Esegue trasmissione/ricezione usando descrittori (buffer e frame)

Scrive esiti e flag di completamento in memoria

Genera interrupt o segnali di stato quando richiesto

Schizzo dei collegamenti più importanti

┌──────────────────────────┐ │ CPU host │ │ driver + allocazione RAM │ └───────────┬──────────────┘ │ Bus host (I/O o memory-mapped) │ + segnali: RD/WR, IRQ, CA, RESET ▼ ┌───────────────┐ │ Intel 82586 │ │ LAN coprocess.│ │ DMA + CU/RU │ └──────┬────────┘ │ Accesso DMA a RAM (buffer + descrittori) ▼ ┌──────────────────────────┐ │ RAM condivisa │ │ - SCP/ISCP/SCB │ │ - Command blocks (CB) │ │ - Tx buffer descriptors │ │ - Rx frame/buffer desc. │ │ - Packet buffers │ └──────────────────────────┘ ▲ │ dati di rete (tx/rx) via MAC/PHY path ▼ ┌──────────────────────────────┐ │ Transceiver / MAU + magnetics │ │ (interfaccia fisica Ethernet) │ └──────────────┬───────────────┘ ▼ Rete Ethernet

Dettagli operativi importanti (driver e prestazioni)

1) Liste e descrittori come “contratto” tra CPU e chip

Il driver prepara catene di descrittori per:

Trasmissione: comando → puntatori ai buffer → stato completamento

Ricezione: frame descriptor → buffer descriptor → buffer pronti a essere riempiti

Il coprocessore “consuma” descrittori pronti, aggiorna flag e passa al successivo. Questo consente pipeline e riduce overhead di interrupt se il driver usa batching.

2) Concorrenza e sincronizzazione

La CPU può continuare a eseguire mentre il coprocessore lavora, ma ci sono punti in cui serve sincronizzazione:

Quando si deve riutilizzare un buffer non ancora “liberato” dal chip

Quando si aggiornano puntatori di lista: servono regole rigorose di ownership e ordering (barriere/memoria, a seconda della piattaforma)

Quando il chip segnala “busy”, “no resources” o condizioni analoghe via status/interrupt

3) Banda memoria come collo di bottiglia

La velocità reale dipende molto da:

Latenza e banda della RAM condivisa

Contesa sul bus con la CPU

Dimensionamento e disposizione di buffer e descrittori (cache locality e frammentazione)

4) Inizializzazione “a root pointer”

Nei controller di questa famiglia è tipico un flusso in cui il driver imposta una radice (pointer di configurazione) che porta alla control structure principale; il chip la legge all’avvio e poi opera sulle liste definite. (Il dettaglio dei nomi e del layout varia tra generazioni, ma il pattern SCP/ISCP/SCB è ricorrente nel 82586 e nella famiglia correlata.)

Tabella 1 – Dati di identificazione e specifiche (bilingue)

| Parametro / Parameter | Valore e note / Value and notes |

|---|---|

| Ruolo / Role | Coprocessore LAN Ethernet con modello a memoria condivisa / Ethernet LAN coprocessor using a shared-memory model |

| Standard / Standard | IEEE 802.3 Ethernet (contesto storico 10 Mb/s) / IEEE 802.3 Ethernet (historical 10 Mb/s context) |

| Trasferimenti / Transfers | DMA per muovere frame e buffer tra RAM e rete / DMA to move frames and buffers between RAM and the network |

| Parallelismo / Parallelism | CPU orchestra, coprocessore esegue in autonomia con aggiornamenti di stato / CPU orchestrates, coprocessor runs autonomously and writes status |

| Gestione buffer / Buffer management | Descrittori e liste in RAM (comandi, tx, rx) / RAM-based descriptors and lists (commands, tx, rx) |

Tabella 2 – Strutture di memoria condivisa e flusso (bilingue)

| Struttura / Structure | Scopo operativo / Operational purpose |

|---|---|

| SCP/ISCP (root pointers) | Puntatori di configurazione/inizializzazione verso la control structure / Initialization pointers to the main control structure |

| SCB (system control block) | Stato e comandi “globali” tra CPU e chip (run/stop, stato unità) / Global CPU–chip control and status (run/stop, unit status) |

| CBL (command block list) | Lista di comandi che il chip percorre ed esegue / List of commands the chip walks and executes |

| RFA (receive frame area) | Area/liste per ricezione: frame/buffer descriptor + buffer / Receive area: frame/buffer descriptors plus buffers |

| Channel attention + interrupt | Meccanismo per notificare nuovi comandi e segnalare completamenti/eventi / Mechanism to notify new work and signal completions/events |

Caratteristiche.

Perform Complete CSMA/CD Medium Access Control Function Independently of CPU

- High Level Command Interface

Supports Established and Emerging LAN Standards

- IEE 802.3/Ethernet (10BASE5)

- IEE 802.3/Cheapernet (10BASE2)

- IEE 802.3/StarLAN (1BASE5)

- Proposed 10BASE-T

- Proposed 10BASE-F

- Proprietary CSMA/CD Networks up to 10 Mb/s

On-Chip Memory Management

- Automatic Buffer Chaining

- Buffer Reclaim After Receipt of Bad Frames

- Save Bad frames, Optionally

Interface to 8 bit and 16 bit Microprocessors

Supports Minimum Component Systems

- Shared Bus Configuration

- Interface to 80186 and 80188 Microprocessors Without Glue

Supports High-Performance Systems

- Bus-Master, with On-Chip DMA

- 5 MB/s Bus Bandwith

- Compatibility with Dual-Port Memory

- Back-to-Back Frame Reception at 10 Mb/s

| Evaluate |