| "Descrizione" by RS232 (2013 pt) | 2026-Feb-03 09:59 |

Review Consensus: 13 Rating: 6.5 Number of users: 2

| Evaluation | N. Experts | Evaluation | N. Experts |

|---|---|---|---|

| 1 | 6 | ||

| 2 | 7 | ||

| 3 | 8 | ||

| 4 | 9 | ||

| 5 | 10 |

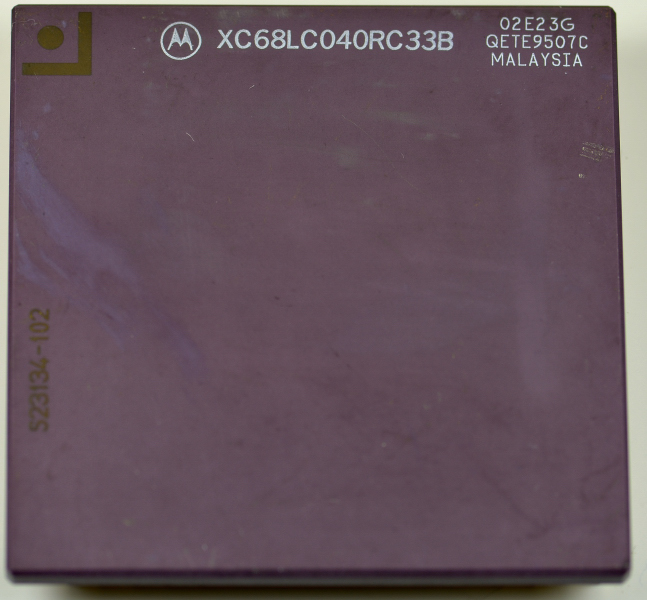

Motorola XC68LC040RC33B (68040) – CPU 32 bit che sostituì il 68030, con cache e pipeline a sei stadi, nella variante LC senza FPU

Definizione

Il Motorola XC68LC040RC33B appartiene alla famiglia 68040, il microprocessore che sostituì il precedente 68030 nella linea 68k. Il 68040 rappresenta un salto generazionale perché integra più funzioni “di sistema” direttamente nel core: cache on-chip, una microarchitettura completamente pipeline (a sei stadi) e, nelle versioni standard, anche la FPU (floating point unit) integrata.

Nel caso specifico, la sigla LC identifica la variante “low-cost” senza FPU: quindi, pur essendo un 68040, non include l’unità in virgola mobile interna. È coerente con l’osservazione sul modello XC68LC040RC25, che risulta “stranamente” privo di FPU: non è un’anomalia, ma una caratteristica di famiglia della variante LC.

Da 68030 a 68040: cosa cambia in pratica

Il passaggio da 68030 a 68040 non è solo un incremento di clock: impatta direttamente sul modo in cui il sistema esegue codice e gestisce memoria.

Punti pratici principali:

Maggiore integrazione nel processore (riduzione della dipendenza da coprocessori esterni per alcune funzioni).

Cache on-chip per ridurre la latenza media degli accessi a istruzioni e dati.

Pipeline a sei stadi per aumentare il throughput (più istruzioni “in volo” contemporaneamente).

Cache e pipeline a sei stadi: effetto sulle prestazioni

La presenza di cache e pipeline rende il comportamento più “moderno” rispetto al 68030:

La cache riduce i cicli di attesa dovuti a RAM/ROM più lente rispetto al core.

La pipeline a sei stadi migliora il parallelismo temporale interno: mentre un’istruzione è in esecuzione, le successive possono essere decodificate/preparete, aumentando l’IPC effettivo quando il flusso è regolare e la memoria risponde bene.

In pratica, il 68040 tende a beneficiare molto di carichi “ben localizzati” (loop, codice che sfrutta cache) e di un sottosistema memoria ben progettato.

FPU integrata nel 68040 e assenza nella variante LC

Il 68040 “pieno” integra una FPU interna: questo permette calcoli in virgola mobile senza un coprocessore esterno, con benefici importanti in applicazioni tecniche, CAD, grafica 3D e software scientifico.

La variante XC68LC040 è invece priva di FPU:

Il codice floating point non può essere eseguito in hardware dalla CPU.

A seconda della piattaforma, la gestione può avvenire tramite emulazione software o tramite soluzioni esterne (quando previste).

Il risultato pratico è che le applicazioni che usano pesantemente floating point possono mostrare un degrado prestazionale significativo rispetto a un 68040 con FPU.

Speed grade: RC33B vs RC25

Le sigle finali sono tipicamente legate alla frequenza massima:

RC33B: variante con clock nominale fino a 33 MHZ (stepping/revisione “B”).

RC25: variante fino a 25 MHZ.

In pratica, a parità di piattaforma, il clock incide, ma cache/pipeline e (soprattutto) presenza della FPU possono contare più del solo incremento di frequenza in carichi reali.

Impieghi noti: workstation e home computer di fascia alta

Il 68040 (incluse varianti) è stato utilizzato in sistemi dove servivano prestazioni superiori alla generazione 68030:

Apple Macintosh Quadra e Macintosh Performa (famiglie con modelli basati su 68040 e varianti).

Workstation e sistemi UNIX di classe 68k (in base a configurazioni e vendor).

Amiga 4000, dove il 68040 era una delle CPU di riferimento nelle configurazioni più performanti.

Schizzo dei collegamenti più importanti

bus di sistema (indirizzi/dati/controllo) + sottosistema memoria ┌──────────────────────────────────────────────────────────┐ │ chipset / controller di sistema │ │ RAM/ROM, I/O, interrupt, timing, espansioni │ └───────────────────────────────┬──────────────────────────┘ │ ▼ ┌─────────────────────────────┐ │ Motorola XC68LC040RC33B │ │ core 68040, cache on-chip │ │ pipeline a sei stadi │ │ variante LC: senza FPU │ └─────────────┬───────────────┘ │ ├────────► RAM/ROM (prestazioni influenzate da cache e timing) └────────► I/O (video, storage, rete, bus di espansione)

Tabella 1 – Dati di identificazione e specifiche

| Caratteristica | Valore indicativo |

|---|---|

| Dispositivo | Motorola XC68LC040RC33B |

| Famiglia | 68040 (successore del 68030) |

| Classe | Microprocessore 32 bit (famiglia 68k) |

| Clock nominale | 33 MHZ (RC33B) |

| Pipeline | Sei stadi |

| Cache | Cache on-chip (istruzioni e dati) |

| FPU | Assente nella variante LC |

| Variante correlata citata | XC68LC040RC25 (25 MHZ, variante LC senza FPU) |

Tabella 2 – Aspetti operativi e progettuali

| Aspetto | Significato pratico |

|---|---|

| Sostituzione del 68030 | Miglioramenti architetturali oltre al clock: cache, pipeline e maggiore integrazione |

| Cache on-chip | Riduce l’impatto della latenza memoria e migliora il throughput in codice con buona località |

| Pipeline a sei stadi | Aumenta il parallelismo interno e le prestazioni medie su flussi regolari |

| FPU integrata (68040 “pieno”) | Floating point in hardware, utile per grafica 3D e applicazioni tecniche |

| Variante LC senza FPU | Floating point demandato a emulazione o soluzioni esterne: possibile calo prestazionale in carichi FP |

| Impieghi tipici | Sistemi Apple, workstation UNIX 68k, Amiga 4000 |

| Evaluate |