| "Descrizione" by Al222 (24878 pt) | 2026-Feb-03 10:02 |

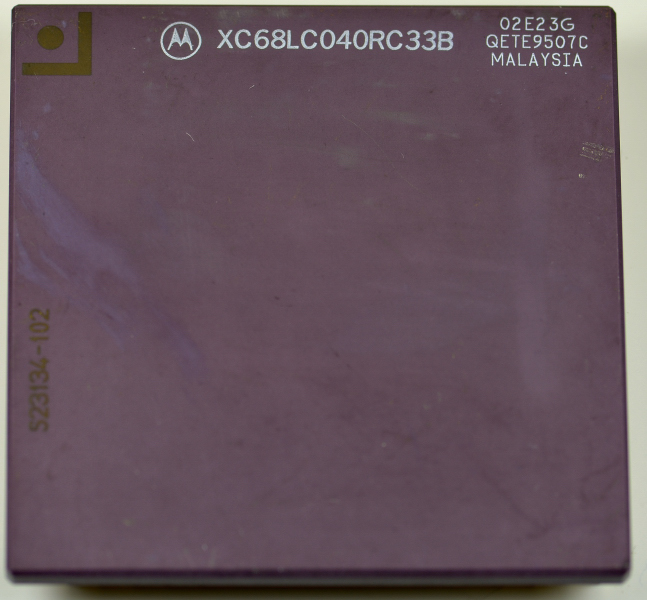

Motorola XC68LC040RC33B (68040) – 32-bit CPU that replaced the 68030, with cache and a six-stage pipeline, in the LC variant without an FPU

Definition

The Motorola XC68LC040RC33B belongs to the 68040 family, the microprocessor that replaced the earlier 68030 within the 68k line. The 68040 represents a generational step because it integrates more “system-level” functions directly into the core: on-chip cache, a fully pipelined microarchitecture (six stages), and—on standard versions—an integrated FPU (floating point unit).

In this specific case, the LC suffix identifies the low-cost variant without an FPU: therefore, while it is a 68040, it does not include the internal floating-point unit. This matches the note about the XC68LC040RC25 being “strangely” without an FPU: it is not an anomaly, but a defining characteristic of the LC family.

From 68030 to 68040: what changes in practice

The transition from 68030 to 68040 is not just a clock increase; it directly affects how the system executes code and handles memory.

Key practical points:

Higher integration within the processor (reduced reliance on external coprocessors for some functions).

On-chip cache to reduce average instruction/data access latency.

A six-stage pipeline to increase throughput (more instructions “in flight” simultaneously).

Cache and six-stage pipeline: performance impact

The presence of cache and pipeline makes the behavior more “modern” than the 68030:

The cache reduces stalls caused by RAM/ROM being slower than the core.

The six-stage pipeline improves internal temporal parallelism: while one instruction executes, subsequent ones can be fetched/decoded/prepared, improving effective IPC when the flow is regular and memory responds well.

In practice, the 68040 benefits strongly from workloads with good locality (loops, cache-friendly code) and from a well-designed memory subsystem.

Integrated FPU in the 68040 and its absence in the LC variant

A “full” 68040 integrates an internal FPU, enabling floating-point computation without an external coprocessor, with major benefits for technical applications, CAD, 3D graphics, and scientific software.

The XC68LC040 variant instead lacks the FPU:

Floating-point code cannot be executed in hardware by the CPU.

Depending on the platform, handling is done via software emulation or external solutions (where provided).

The practical result is that floating-point-heavy applications can suffer a significant performance drop compared to an FPU-equipped 68040.

Speed grade: RC33B vs RC25

The suffixes are typically tied to the maximum rated clock:

RC33B: variant rated up to 33 MHZ (with “B” indicating a stepping/revision).

RC25: variant rated up to 25 MHZ.

In practice, clock matters, but cache/pipeline and (especially) FPU presence can matter more than frequency alone in real workloads.

Known deployments: high-end workstations and home computers

The 68040 (including its variants) was used in systems where higher performance than the 68030 generation was required:

Apple Macintosh Quadra and Macintosh Performa (families with models based on the 68040 and variants).

68k-class UNIX workstations and systems (depending on vendor and configuration).

Amiga 4000, where the 68040 was one of the reference CPUs in higher-end configurations.

Sketch of the most important connections

system bus (address/data/control) + memory subsystem ┌──────────────────────────────────────────────────────────┐ │ chipset / system controller │ │ RAM/ROM, I/O, interrupts, timing, expansions │ └───────────────────────────────┬──────────────────────────┘ │ ▼ ┌─────────────────────────────┐ │ Motorola XC68LC040RC33B │ │ 68040 core, on-chip cache │ │ six-stage pipeline │ │ LC variant: no FPU │ └─────────────┬───────────────┘ │ ├────────► RAM/ROM (performance influenced by cache and timing) └────────► I/O (video, storage, networking, expansion bus)

Table 1 – Identification data and specifications

| Characteristic | Indicative value |

|---|---|

| Device | Motorola XC68LC040RC33B |

| Family | 68040 (successor to the 68030) |

| Class | 32-bit microprocessor (68k family) |

| Nominal clock | 33 MHZ (RC33B) |

| Pipeline | Six stages |

| Cache | On-chip cache (instruction and data) |

| FPU | Absent in the LC variant |

| Related cited variant | XC68LC040RC25 (25 MHZ, LC variant without FPU) |

Table 2 – Operational and design considerations

| Aspect | Practical meaning |

|---|---|

| Replacement of the 68030 | Architectural improvements beyond clock: cache, pipeline, and higher integration |

| On-chip cache | Reduces memory-latency impact and improves throughput for locality-friendly code |

| Six-stage pipeline | Increases internal parallelism and average performance on regular instruction flows |

| Integrated FPU (full 68040) | Hardware floating point, useful for 3D graphics and technical applications |

| LC variant without FPU | Floating point handled by emulation or external solutions: potential performance drop on FP-heavy workloads |

| Typical deployments | Apple systems, 68k UNIX workstations, Amiga 4000 |

| Evaluate |