| "Descrizione" by CPU1 (1876 pt) | 2026-Feb-02 18:49 |

Review Consensus: 7 Rating: 7 Number of users: 1

| Evaluation | N. Experts | Evaluation | N. Experts |

|---|---|---|---|

| 1 | 6 | ||

| 2 | 7 | ||

| 3 | 8 | ||

| 4 | 9 | ||

| 5 | 10 |

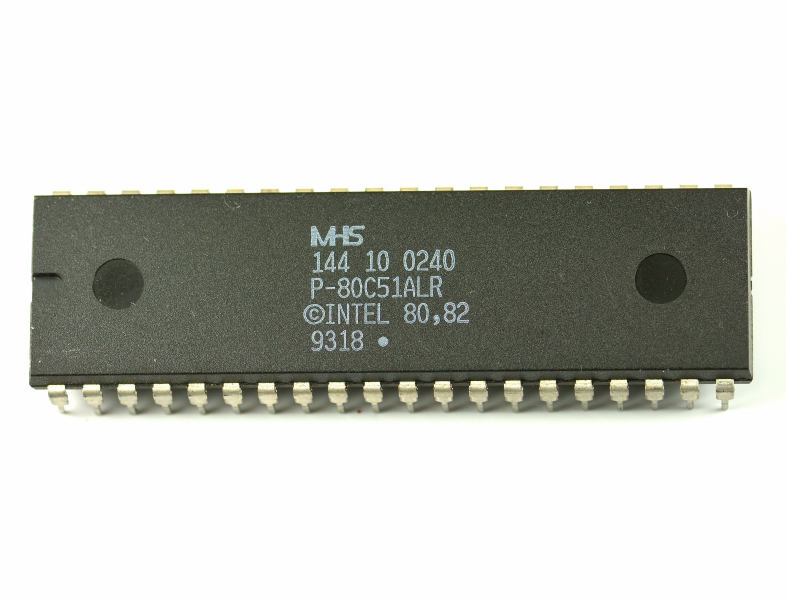

MHS P-80C51

Definizione

Il MHS P-80C51 è un MICROCONTROLLER 8 BIT compatibile MCS-51 (core tipo 8051) realizzato in tecnologia CMOS, progettato per sistemi embedded dove servono I/O paralleli, temporizzazioni hardware e comunicazione seriale con un consumo contenuto.

La variante “P-80C51” integra ROM programma on-chip e una RAM interna per i dati; inoltre, pur essendo un single-chip, può indirizzare memoria esterna (programma e dati) fino a 64K per ciascuno spazio, consentendo progetti scalabili (da “tutto on-chip” a sistemi con memoria e periferiche esterne).

Memorie integrate: 4K × 8 ROM e 128 × 8 RAM

ROM 4K × 8: contiene il firmware (programma) residente nel chip. È adatta a controlli compatti, logiche a stati, gestione I/O e protocolli semplici.

RAM 128 × 8: è la memoria dati interna usata per variabili, stack, buffer piccoli e dati “caldi” con latenza minima.

Quando l’applicazione richiede firmware o dati più grandi, si ricorre alla memoria esterna: la ROM interna resta utile per versioni base o per firmware “core” in sistemi ibridi.

Tre contatori/timer a 16 bit (time-base e misure)

Il dispositivo include THREE 16 BIT COUNTER/TIMERS, utili per:

Time-base di sistema (tick periodici).

Misure di durata e generazione di ritardi deterministici.

Conteggio eventi (impulsi esterni) e temporizzazione di protocolli.

A livello pratico, la presenza di tre timer riduce la necessità di time-sharing software e rende più semplice gestire contemporaneamente seriale, I/O e sequenze temporizzate.

4 porte a 8 bit: 32 linee I/O

Le 4 porte a 8 bit forniscono complessivamente 32 linee I/O programmabili. In uso reale servono per:

Interfaccia diretta a sensori digitali, tasti, LED, relè (tramite driver), latch e bus di espansione.

Funzioni alternate e/o impiego come bus esterno multiplexato (tipico della famiglia MCS-51 quando si usano memorie esterne).

Seriale: comunicazioni multiprocessore, espansione I/O, UART full duplex

È presente una porta seriale integrata utilizzabile come:

Canale per comunicazioni multiprocessore (indirizzamento/filtraggio su bus condiviso).

Link per espansione I/O (riduzione cablaggi paralleli con dispositivi seriali).

UART full duplex per diagnostica, console di servizio o collegamento a periferiche (tramite transceiver esterni se necessario).

Boolean processor (elaborazione a livello di bit)

La dicitura BOOLEAN PROCESSOR indica la disponibilità di istruzioni e meccanismi hardware orientati alla manipolazione di singoli bit:

Operazioni logiche e test su bit in aree dedicate (bit-addressable).

Gestione efficiente di flag, maschere, segnali di stato e I/O bit-wise.

In pratica, molte logiche di controllo (interlock, stati, condizioni) risultano più compatte e veloci rispetto a un approccio puramente “byte-oriented”.

Full static operation (Hz → MHZ)

La FULL STATIC OPERATION significa che la logica interna può operare con clock riducibile fino a frequenze molto basse (anche prossime a 0), senza perdere lo stato dei registri e della RAM interna. Questo abilita strategie di risparmio energetico basate sulla riduzione del clock e si integra bene con le modalità IDLE/POWER DOWN tipiche di questa classe di microcontroller.

Low voltage: 2,7 V – 5,5 V a 16 MHZ

Il dispositivo è indicato per funzionare con alimentazione 2,7 V – 5,5 V a 16 MHZ (versione low-voltage). Il vantaggio pratico è la compatibilità con sistemi a batteria o alimentazioni “non 5 V pure”, mantenendo prestazioni utili senza dover necessariamente usare regolazioni strette o componenti di potenza più complessi.

Memory addressing capability: 64K ROM e 64K RAM (memorie esterne)

Il P-80C51 supporta l’indirizzamento di:

64K di spazio ROM esterno (spazio programma/codice).

64K di spazio RAM esterno (spazio dati esterno, spesso chiamato XDATA).

Questo consente:

Firmware più grande della ROM interna (ad esempio EPROM/FLASH esterna).

Buffer e aree dati estese (RAM esterna) e periferiche memory-mapped.

Schizzo dei collegamenti più importanti

┌──────────────────────────────┐ │ EPROM / FLASH │ │ (programma esterno fino 64K)│ └──────────────┬───────────────┘ │ bus codice (addr/data + control) ▼ ┌──────────────────┐ │ MHS P-80C51 │ │ MCU 8 BIT CMOS │ │ ROM 4K×8 │ │ RAM 128×8 │ │ 4×8 I/O PORTS │ │ 3× TIMER 16 BIT │ │ UART + OSC/CLK │ └───────┬──────────┘ │ ├────────► I/O → sensori / driver / latch / LED / relè │ ├────────► UART → multiprocessore / espansione / debug │ └────────► RAM esterna (opz.) → fino 64K (spazio dati)

Tabella 1 – Dati di identificazione e specifiche (italiano)

| Caratteristica | Valore indicativo |

|---|---|

| Dispositivo | MHS P-80C51 |

| Classe | MICROCONTROLLER 8 BIT (famiglia MCS-51, core tipo 8051) |

| Tecnologia | CMOS |

| ROM on-chip | 4K × 8 |

| RAM on-chip | 128 × 8 |

| Porte I/O | 4 × 8 BIT (32 linee) |

| Timer/counter | THREE 16 BIT COUNTER/TIMERS |

| Seriale | Porta seriale: multiprocessore / espansione I/O / UART full duplex |

| Funzioni logiche | BOOLEAN PROCESSOR (bit-addressable) |

| Alimentazione | 2,7 V – 5,5 V a 16 MHZ |

| Indirizzamento memorie esterne | 64K ROM + 64K RAM |

Tabella 2 – Aspetti operativi e progettuali (italiano)

| Aspetto | Significato pratico |

|---|---|

| FULL STATIC OPERATION | Possibilità di ridurre il clock per risparmio energetico senza perdere lo stato interno |

| ROM 4K×8 | Firmware compatto “on-chip”; riduce componenti esterni in applicazioni semplici |

| RAM 128×8 | Stack e variabili critiche; tipicamente si aggiunge RAM esterna per buffer grandi |

| 3 timer a 16 bit | Gestione simultanea di tick, misure e temporizzazioni di protocolli |

| 32 linee I/O | Alta densità I/O; possibile uso come bus esterno in sistemi con memorie esterne |

| Seriale multiprocessore/UART | Comunicazione robusta su bus condivisi o link full duplex per debug/periferiche |

| 2,7–5,5 V @ 16 MHZ | Adatto a sistemi low-voltage mantenendo buone prestazioni |

| 64K ROM + 64K RAM esterni | Scalabilità: firmware/dati estesi e periferiche memory-mapped |

| Evaluate |