| "Descrizione" by CPU1 (1882 pt) | 2026-Jan-29 09:22 |

Review Consensus: 14 Rating: 7 Number of users: 2

| Evaluation | N. Experts | Evaluation | N. Experts |

|---|---|---|---|

| 1 | 6 | ||

| 2 | 7 | ||

| 3 | 8 | ||

| 4 | 9 | ||

| 5 | 10 |

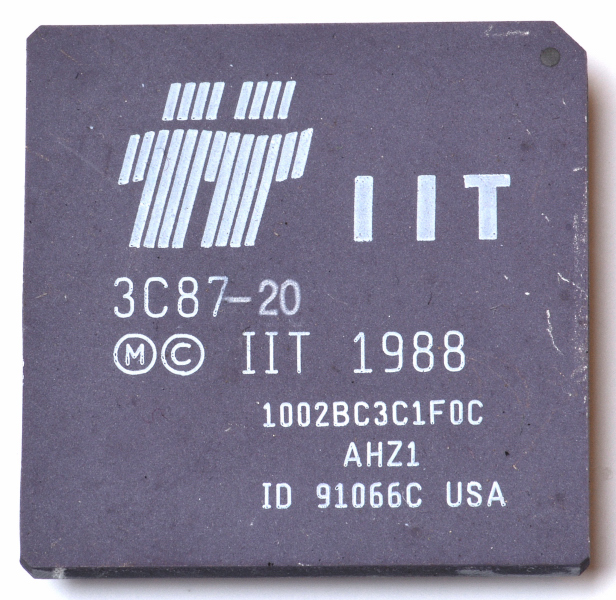

Il coprocessore matematico veniva affiancato al microprocessore CPU per svolgere funzioni veloci matematiche quali addizioni, sottrazioni, moltiplicazioni, divisioni, esponenziali, logaritmiche, trigonometriche e calcoli in virgola mobile.

Utilizzato da Intel, Cyrix, ITT, Motorola, Apple e dalla maggior parte dei produttori di circuiti integrati dell'epoca.

Nato nel 1980 prodotto da Intel (8087), la generazione dei coprocessori matematici scompare negli anni '90, integrato nelle CPU.

Un coprocessore matematico (o FPU, floating-point unit) è un processore specializzato che affianca la CPU per eseguire più rapidamente (e con maggiore flessibilità numerica) operazioni come aritmetica in virgola mobile, funzioni trascendenti (es. seno, coseno, tangente), radici, logaritmi e calcoli su numeri reali ad ampia dinamica. Nel caso “classico” dell’Intel 8087, il coprocessore lavora in tandem con CPU come 8086/8088: la CPU gestisce il flusso del programma, mentre l’8087 esegue le operazioni matematiche pesanti.

Contesto storico e perché nasce

Negli anni dei primi PC e dei sistemi basati su 8086/8088, la CPU poteva fare calcoli in intero in modo ragionevole, ma la virgola mobile in software era lenta e impegnava molte istruzioni. Un coprocessore dedicato come l’8087 portava vantaggi pratici in applicazioni quali: CAD, calcolo scientifico, grafica tecnica, simulazioni, elaborazioni numeriche e (più tardi) alcune routine di rendering o modellazione.

Come lavora un 8087 in un sistema 8086/8088

Il punto chiave è che l’8087 non “rimpiazza” la CPU: la CPU decodifica le istruzioni, e quando incontra un’istruzione destinata alla FPU, la CPU e l’8087 si coordinano. In pratica:

La CPU esegue il programma e, quando necessario, emette istruzioni “ESC” (escape) che identificano operazioni FPU.

L’8087 “ascolta” il bus e aggancia quelle istruzioni, poi esegue internamente l’operazione.

Se l’operazione richiede dati in memoria, l’8087 coopera con la CPU per leggere/scrivere, usando i segnali di arbitraggio del bus.

La CPU può continuare con istruzioni successive, ma spesso serve sincronizzazione (attese) quando si deve usare subito il risultato.

Questo modello è un antenato dei concetti moderni di esecuzione parallela e “accelerazione” hardware, anche se con vincoli e sincronizzazioni molto più evidenti.

Schizzo concettuale dei collegamenti e del flusso

┌───────────────┐ Programma/istr. │ 8086/8088 │ + controllo ──►│ CPU (control) │ └──────┬────────┘ │ Bus (indirizzi/dati/controllo) │ + istruzioni ESC osservate ▼ ┌───────────────┐ Calcolo numerico │ 8087 │ in virgola │ coprocessore │ mobile └──────┬────────┘ │ ▼ Memoria / risultati

Architettura e modello di programmazione dell’8087

L’8087 implementa una FPU con un modello a stack di registri (storicamente noto come stack a 8 livelli, con registri spesso indicati come ST(0)…ST(7)). Questo influisce su come si scrive l’assembly: molte istruzioni operano implicitamente sul “top of stack” (ST(0)), combinandolo con un altro elemento dello stack o con un operando in memoria.

Aspetti tipici del modello FPU “stile 8087”:

Stack di registri: push/pop impliciti in molte istruzioni.

Formato esteso interno: l’unità può usare una precisione interna più ampia di quella memorizzata in RAM, migliorando alcuni calcoli intermedi.

Controllo del comportamento numerico: modalità di arrotondamento, gestione di overflow/underflow, e mascheramento delle eccezioni (dipende dal controllo FPU).

Che tipi di operazioni accelera

Un coprocessore matematico tipo 8087 accelera soprattutto:

Addizione, sottrazione, moltiplicazione, divisione in virgola mobile.

Conversioni tra interi e floating-point.

Radice quadrata e operazioni correlate.

Funzioni trascendenti (in alcune famiglie/istruzioni): utili per trigonometria e logaritmi.

Nella pratica, il guadagno prestazionale dipende dal mix di operazioni e da quanta sincronizzazione è necessaria tra CPU e coprocessore.

Sincronizzazione e punti critici

In un’architettura a coprocessore separato, la CPU e la FPU possono lavorare “in parallelo” solo fino a un certo punto. I colli di bottiglia tipici sono:

Dipendenze sui risultati: se la CPU deve usare subito l’esito della FPU, deve attendere.

Accessi a memoria: letture/scritture coordinate via bus introducono latenza.

Gestione delle eccezioni: condizioni numeriche speciali possono richiedere controlli aggiuntivi o configurazione della maschera.

Tabella 1 – Caratteristiche chiave

| Caratteristica | Descrizione |

|---|---|

| Ruolo | Acceleratore per calcoli in virgola mobile e funzioni matematiche |

| Integrazione | Coprocessore esterno che collabora con CPU 8086/8088 |

| Modello registri | Stack di registri FPU (operazioni spesso implicite su ST(0)) |

| Dati | Supporto a formati floating-point, spesso con precisione interna estesa |

| Vantaggi tipici | Maggiore velocità e coerenza numerica rispetto a emulazione software |

| Limiti tipici | Sincronizzazione CPU/FPU e latenza bus nei trasferimenti |

Tabella 2 – Concetti di programmazione e sistema

| Concetto | Implicazione pratica |

|---|---|

| Istruzioni FPU (ESC) | La CPU emette istruzioni che l’FPU intercetta ed esegue |

| Attese/sincronizzazione | Necessarie quando il risultato serve immediatamente |

| Eccezioni floating-point | Gestione via controllo FPU (maschere, status) |

| Beneficio reale | Dipende dal carico: più calcolo numerico ⇒ più vantaggio |

Evoluzione e “equivalenti moderni”

Con il tempo, la FPU è stata integrata direttamente nella CPU (anziché essere un chip separato), riducendo latenza e complessità di sincronizzazione. Oggi, oltre alla FPU integrata, molte CPU includono estensioni vettoriali (SIMD) e acceleratori dedicati (es. per DSP, AI) che riprendono lo stesso principio: spostare calcoli intensivi su unità più adatte.

Mini-glossario

Coprocessore: chip ausiliario che esegue una classe specifica di operazioni per alleggerire la CPU.

FPU: unità per calcoli in virgola mobile.

Virgola mobile: rappresentazione dei numeri reali con ampia dinamica, utile per scientifico/tecnico.

Stack di registri: insieme di registri usati come pila, con un elemento “in cima” su cui operano molte istruzioni.

Sincronizzazione: meccanismi con cui la CPU attende o coordina l’avanzamento della FPU.

| Evaluate |